# РАДИОТЕХНИКА, ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА, ПРИБОРОСТРОЕНИЕ И СВЯЗЬ

Научная статья

УДК 621.391

URL: <a href="https://trudymai.ru/published.php?ID=186309">https://trudymai.ru/published.php?ID=186309</a>

EDN: https://www.elibrary.ru/PILPJN

# РАЗРАБОТКА МИКРОСХЕМ КОДЕРА И ДЕКОДЕРА СІ-ВСН

Алексей Станиславович Волков $^{1}$  $\boxtimes$ , Алексей Викторович Солодков $^{2}$ , Иван Андреевич Захаров $^{3}$

1,2,3 Национальный исследовательский университет «Московский институт

электронной техники»

Москва, Зеленоград, Россия

<sup>1</sup>⊠<u>leshvol@mail.ru</u>

<sup>2</sup>solodkov aw@mail.ru

<sup>3</sup>wanueschok@mail.ru

Аннотация. В работе описана разработка микросхем кодера и декодера СІ-ВСН (Continuously Interleaved ВСН) для систем высокоскоростной передачи данных. Разработано Verilog-описание кодера и декодера, выполнен синтез в стандартных ячейках и синтезирована топология микросхем. Основные параметры разработанной микросхемы: 30 и 150 тыс. стандартных ячеек для кодера и декодера соответственно, тактовая частота до 100 МГц, пропускная способность 1,6 Гбит/с. Показано, что разработанный декодер обладает невысокой аппаратной сложностью и может быть

интегрирован в состав систем-на-кристалле (SoC).

**Ключевые слова:** CI-BCH, кодер, декодер, FEC, Verilog, стандартные ячейки, топология.

**Для цитирования:** Волков А.С., Солодков А.В., Захаров И.А. Разработка микросхем кодера и декодера CI-ВСН // Труды МАИ. 2025. № 144.

URL: <a href="https://trudymai.ru/published.php?ID=186309">https://trudymai.ru/published.php?ID=186309</a>

# RADIO ENGINEERING, COMPUTER ENGINEERING, INSTRUMENTATION AND COMMUNICATIONS

Original article

# DESIGN OF CI-BCH ENCODER AND DECODER INTEGRATED CIRCUITS

Alexey S. Volkov¹⋈, Alexey V. Solodkov², Iwan A. Zaharow³

<sup>1,2,3</sup>National Research University of Electronic Technology, Moscow, Zelenograd, Russia

<sup>1</sup>⊠leshvol@mail.ru

<sup>2</sup>solodkov\_aw@mail.ru

<sup>3</sup>wanueschok@mail.ru

Abstract. This paper describes the development of CI-BCH (Continuously Interleaved BCH) encoder and decoder integrated circuits for high-performance data transmission systems. A Verilog description of the encoder and decoder was developed, standard-cell synthesis was performed, and the integrated circuit topology was synthesized. The key parameters of the developed integrated circuit are 30,000 and 150,000 standard cells for the encoder and decoder, respectively, a clock frequency of up to 100 MHz, and a throughput

of 1.6 Gbps. It is demonstrated that the developed decoder has low hardware complexity and can be integrated into systems-on-chip (SoC).

Keywords: CI-BCH, encoder, decoder, FEC, Verilog, standard cells, topology.

For citation: Volkov A.S., Solodkov A.V., Zaharow I.A, Design of CI-BCH encoder and decoder integrated circuits // Trudy MAI. 2025. № 144. URL: https://trudymai.ru/published.php?ID=186309

#### Введение

Современные аэрокосмические системы столкнулись с экспоненциальным ростом объемов передаваемой и обрабатываемой информации [1]. Данные телеметрии, навигации, результаты дистанционного зондирования Земли, а также мультимедийные потоки в системах бортового обслуживания предъявляют повышенные требования к пропускной способности и надежности каналов связи [2]. При этом условия функционирования таких систем характеризуются наличием мощных электромагнитных помех [3], воздействием ионизирующих излучений и строгими ограничениями по массогабаритным показателям, энергопотреблению и надежности [4].

В этих условиях для систем хранения и передачи информации предъявляются высокие требования к скорости передачи данных и вероятности битовых ошибок [5]. Развитие новых сценариев использования систем беспроводной связи, таких как интернет вещей и межмашинное взаимодействие (М2М), повышает требования к ёмкости и устойчивости каналов передачи [6]. Для обеспечения низкой вероятности битовой ошибки в сетях и системах данных применяются линейные блоковые,

свёрточные [7] и другие помехоустойчивые коды [8]. Поиск компромисса между корректирующей способностью, аппаратной сложностью и энергопотреблением кодеров и декодеров остаётся ключевой задачей при проектировании современных бортовых систем связи.

Дополнительным фактором, усложняющим задачу, является активное внедрение оптоволоконных сетей в бортовые системы современных самолетов и космических аппаратов. В оптических системах передачи данных, где скорость передачи данных составляет до 100 Гбит/с применение прямого исправления ошибок является обязательным условием обеспечения требуемого качества передачи, ввиду воздействия на сигналы помех и шумов [9, 10]. Стандартные решения, такие как RS-FEC или коды, рекомендованные ITU-T G.975.1 [11], обеспечивают ограниченный выигрыш от кодирования и не всегда удовлетворяют требованиям по задержке и ресурсоёмкости при стандартном 7% объёме избыточности. В этой связи был предложен усовершенствованный метод — CI-BCH (Continuously Interleaved BCH [12]), обеспечивающий эффективный выигрыш от кодирования порядка 9,3 дБ для вероятности ошибки на бит 10-15, низкую сложность реализации и устойчивость к пакетам ошибок [13].

На сегодняшний день опубликованы результаты моделирования и FPGA-реализаций СІ-ВСН [14], однако данные о реализации на уровне специализированных микросхем (англ. application-specific integrated circuit, ASIC [15]) отсутствуют. Между тем именно интеграция в состав систем-на-кристалле и сетевых чипов является ключевым условием практического применения СІ-ВСН в телекоммуникационном оборудовании [16].

В настоящей работе предоставлено описание маршрута разработки Verilogописание кодера и декодера СІ-ВСН, их синтез в стандартных ячейках и проектирование топологии. Приведены основные характеристики полученных микросхем и обсуждается возможность их использования в системах высокоскоростной передачи данных.

Данные микросхемы можно производить на доступном в России оборудовании, что важно, учитывая, что телекоммуникационные компании России проявляют интерес к отечественным разработкам микроэлектроники [17].

# Описание схемы кодирования СІ-ВСН

В данном разделе кратко излагается математическая основа кодирования предложенной реализации СІ-ВСН. Приводятся ключевые этапы формирования кодовых слов в соответствии с параметрами выбранного кода и принципом непрерывного интерливинга, который обеспечивает требуемую помехоустойчивость [18].

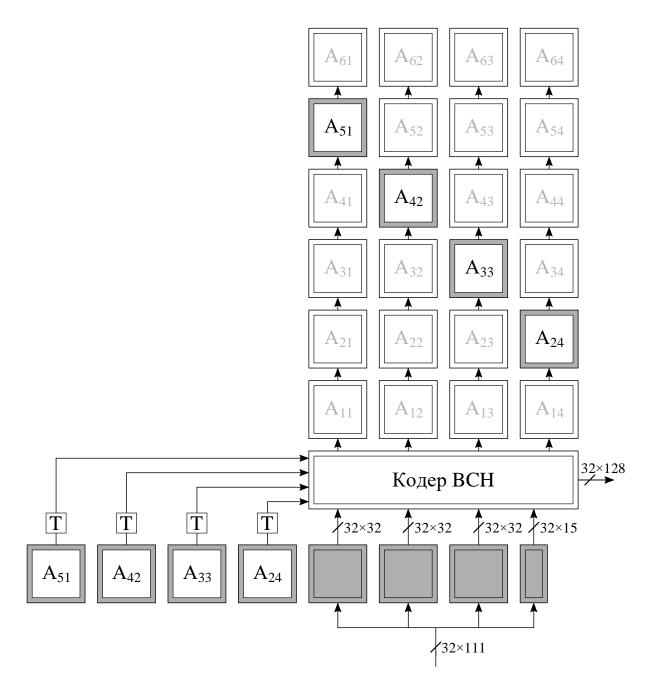

Ниже на рисунке 1 приведена логическая структура кодера. Использованы следующие обозначения:  $A_{ij}$  – блоки памяти размером 32×32, блок с обозначением Т соответствует операции транспонирования, обозначение вида «32×111» обозначает разрядность шины.

Рисунок 1 – Схема кодирования СІ-ВСН

Входной поток данных подаётся во фреймах длиной 3552 бита (на рисунке 1 обозначены серыми прямоугольниками). Далее согласно структуре кода СІ-ВСН каждый фрейм представляется в виде матрицы размером 32×111 бит, где строки формируют исходные блоки, строки, которые затем подвергаются кодированию.

Затем выполняется процедура кодирования помехоустойчивым кодом. На первом этапе фрейм обрабатывается кодером ВСН. Для этого к исходным блокам для

кодирования слева добавляют 4 блока из памяти, предварительно транспонировав их. Далее к блокам, которые вместе представляют массив данных размерностью 32 строки по 239 бит, применяется код ВСН(255,239) с дополнительным битом чётности, обозначаемый далее как ВСН(256,239). После кодирования длина каждой строки равна 256 бит. Таким образом, на выходе формируется 32 строки по 256 бит.

Из полученных кодовых слов выделяются последние 128 бит каждой строки, которые образуют фрагмент размером  $32 \times 128$  бит. Этот массив данных разбивается на четыре квадрата размером  $32 \times 32$  бита, каждый из которых записывается в соответствующие позиции матрицы памяти кодера. При этом реализуется схема сдвига: данные, ранее находившиеся в нижнем ряду блоков ( $A_{11}$ – $A_{14}$ ), последовательно перемещаются вверх (в ряды  $A_{21}$ – $A_{24}$  и далее до  $A_{61}$ – $A_{64}$ ), обеспечивая механизм непрерывного интерливинга.

Часть данных, записанных в верхние блоки ( $A_{11}$ – $A_{14}$ ), одновременно формирует выходной поток кодера и передаётся получателю. Таким образом, на каждом шаге происходит:

- 1) приём нового фрейма данных;

- 2) кодирование с использованием ВСН(256,239);

- 3) обновление блоков памяти с учётом сдвига;

- 4) формирование выходного потока.

# Описание схемы декодирования СІ-ВСН

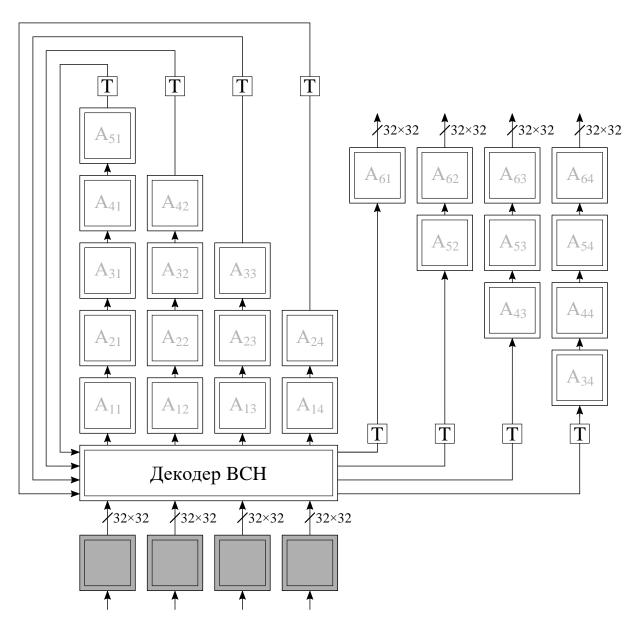

В данном разделе представлено краткое описание классического процесса декодирования СІ-ВСН: вычисление синдромов, определение полинома локатора ошибок и коррекция ошибок, а также особенности восстановления исходного порядка данных после интерливинга. Ниже на рисунке 2 приведена логическая структура декодера.

Рисунок 2 – Схема декодирования СІ-ВСН

Входные данные поступают на декодер фреймами длиной 4096 бит (4 серых квадрата внизу рисунка 2), организованной в виде четырёх блоков размером 32×32 бит каждый. Для восстановления каждого полного кодового слова помимо текущего фрейма используются предыдущие фреймы, сформированные на предыдущих этапах декодирования и хранящиеся в памяти декодера (входы слева от блока декодера). В результате формируются строки длиной 256 бит, соответствующие кодовым словам кода ВСН с дополнительным битом чётности.

Каждая строка передаётся в декодер кода ВСН(256,239). При наличии ошибок декодер выполняет ИХ исправление; если число ошибок превосходит корректирующую способность строка сохраняется без изменений. кода, Исправлению подвергаются как вновь поступившие данные, так и ранее сохранённые блоки памяти. После коррекции обновлённые строки проходят транспонирование и возвращаются в память для участия в последующих шагах обработки.

Обновление памяти декодера сопровождается сдвигом: содержимое нижнего ряда блоков (ячейки  $A_{11}$ – $A_{14}$ ) перемещается вверх по столбцам, а в их место загружаются новые исправленные данные текущего фрейма. Таким образом, реализуется механизм непрерывного интерливинга, позволяющий перераспределять ошибки между последовательными кодовыми словами [18].

Исправленный выходной поток формируется из данных, извлекаемых из верхнего ряда блоков памяти (ячейки  $A_{61}$ – $A_{64}$ ). Полученные данные могут быть дополнительно поданы на вход следующего каскадного декодера аналогичной структуры, что обеспечивает дальнейшее снижение вероятности ошибки за счет итеративного потокового декодирования однотипными декодерами.

# Аппаратная реализация кодера CI-BCH

В этом разделе рассматривается архитектура аппаратного кодера CI-ВСН и принципы его работы в поточном режиме. Описываются основные блоки — входной десериализатор, модули ВСН-кодирования, система буферной памяти и блоки транспонирования, а также механизмы синхронизации, обеспечивающие непрерывную передачу данных и реализацию интерливинга.

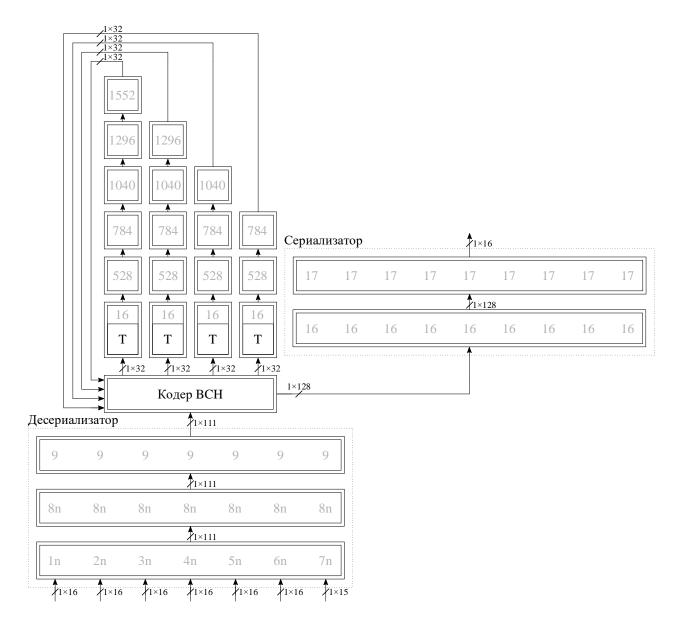

На рисунке 3 и далее принято следующее обозначение: 8n — номер такта, на котором информация от первого фрейма достигает соответствующего блока. При наличии буквы n — середина такта, иначе — начало такта.

Разработанный кодер CI-BCH функционирует в поточном режиме, обеспечивая согласованную обработку входного и выходного потока данных.

Входной интерфейс принимает данные по шине шириной 16 бит по два байта за такт, что требует использования десериализатора [19]. Ввиду того, что все шины, кроме выходной используются раз в 8 тактов, входная шина была обозначена как 7 шин, соответствующих разрядностей. Каждый восьмой такт пропускается.

Входные данные накапливаются в десериализаторе, который каждые восемь тактов формирует блок длиной 111 бит. Сформированные блоки поступают в модуль ВСН-кодера, где выполняется кодирование кода ВСН(256,239). На выходе формируется кодовое слово длиной 128 бит, выдаваемое каждые восемь тактов.

Рисунок 3 – Аппаратная реализация кодера CI-BCH

При реализации схемы кодирования момент транспонирования данных смещён на момент сразу после выхода из кодера ВСН. Таким образом имеется возможность отказаться от использования мультиплексора при подаче данных из памяти в кодер ВСН, что сокращает время загрузки данных [20].

Для реализации механизма интерливинга используются блоки транспонирования (обозначены как «Т»). В аппаратной реализации они имеют иную логику работы. Каждый блок имеет память ёмкостью 32×32 бит и работает непрерывно: на вход каждые восемь тактов поступает новая строка длиной 128 бит,

одновременно на выходе формируется очередная строка для передачи в последующие блоки, в отличие от математической реализации, при которой действие транспонирования выполняется моментально. После заполнения всего массива 32×32 бит выполняется операция транспонирования: содержимое блока целиком передаётся в соседний блок. При этом режим работы остаётся непрерывным — блок, выполняющий запись, продолжает параллельно выдавать накопленные строки, а принимающий блок — выдавать свои строки с тем же периодом.

Таким образом, каждые восемь тактов происходит сдвиг данных на одну строку, а каждые 256 тактов осуществляется передача всего массива с транспонированием. Такой режим обеспечивает непрерывный обмен между блоками хранения и реализует требуемый механизм непрерывного интерливинга СІ-ВСН.

Выходной тракт построен на основе сериализатора [21], который преобразует блоки по 128 бит в поток шириной 16 бит. Каждые восемь тактов формируется новая порция данных.

В результате устройство выполняет последовательное кодирование кодом ВСН с параллельной организацией памяти и транспонированием блоков. Такая архитектура позволяет поддерживать постоянную скорость обработки и реализовать интерливинг кодовых слов, повышающая устойчивость системы к пакетам ошибок [22].

# Аппаратная реализация декодера СІ-ВСН

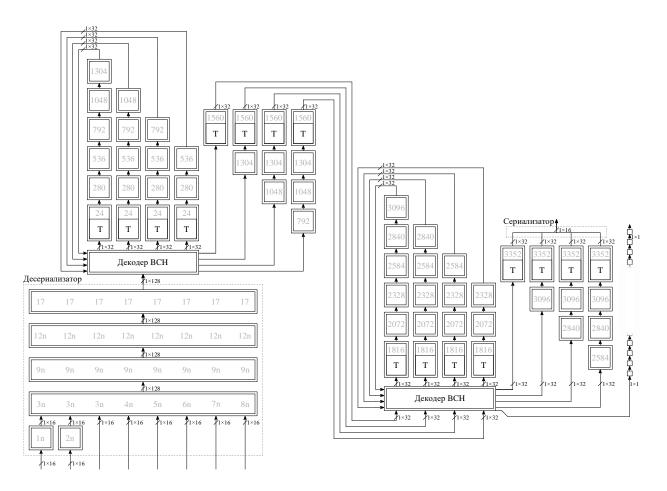

Ниже на рисунке 4 приведена схема аппаратной реализации декодера СІ-ВСН.

Рисунок 4 – Аппаратная реализация декодера CI-BCH

Разработанный декодер СІ-ВСН функционирует в поточном режиме и обеспечивает исправление ошибок в последовательностях длиной 4096 бит, представленных в виде матрицы 32×128 бит. Структура декодера содержит два независимых модуля ВСН-декодера, работающих параллельно, что позволяет выполнять коррекцию сразу на двух стадиях обработки данных.

На вход декодера поступают данные по шине шириной 16 бит. Десериализатор группирует поток в блоки по 128 бит, формируя одну строку каждые восемь тактов.

На рисунке это представлено как 8 параллельных шин разрядности 16, каждая из которых используется раз во 8 тактов, как и все остальные шины, обозначенные на рисунке 4. Таким образом, полный фрейм из 32 строк формируется за 256 тактов.

Основу декодера составляет структура из блоков памяти размером 32×32 бит. Каждые восемь тактов выполняется сдвиг на одну строку (128 бит), которая передаётся в вышестоящие блоки. Управление этим процессом осуществляется стробом sdwig, формируемым в начале каждого 1-го, 9-го, 17-го и т.д. такта. При поступлении сигнала sdwig синхронно обновляется содержимое всей памяти: новые строки из десериализатора и накопленные строки из буферов одновременно подаются на вход ВСН-декодеров.

На первой стадии (по мере продвижения данных по микросхеме) блоки памяти и десериализатор совместно формируют полные 256-битовые кодовые слова (128 бит из текущего входного блока и 128 бит из ранее накопленных данных). Эти кодовые слова поступают в первый ВСН-декодер, который исправляет ошибки в пределах своей корректирующей способности, то есть не более 2-х ошибок [23]. Исправленные строки сразу записываются обратно в память и продолжают участвовать в дальнейших шагах обработки.

Блоки транспонирования работает непрерывно: каждые восемь тактов они принимают строку длиной 128 бит и одновременно выдают строку того же размера.

Когда блок транспонирования полностью заполняется (через 256 тактов), выполняется транспонирование содержимого и его передача в соседний блок. При этом режим работы блоков не прерывается: запись и выдача строк продолжаются параллельно.

После продвижения по памяти слово поступает во второй ВСН-декодер, работающий параллельно с первым. Таким образом, каждая строка проходит через два независимых этапа коррекции. Это повышает вероятность исправления ошибок, в том числе длинных пакетов ошибок, характерных для оптических каналов, что подтверждается моделированием канала связи по модели Гильберта [24].

При этом второй декодер дополнительно выставляет флаг валидности декодированных данных, который движется по памяти параллельно со словом по дополнительному сдвиговому регистру (справа на схеме).

Исправленные данные, находящиеся в верхнем ряду блоков памяти (см рис. 4), направляются в сериализатор. Сериализатор преобразует 128-битовые строки обратно в поток по два байта за такт. При выдаче данных так же выдаётся флаг валидности декодированных данных. Таким образом, выходной интерфейс полностью синхронизирован с входным: каждые восемь тактов формируется новая строка, и декодер работает в режиме постоянного потока без разрывов.

Такая организация – сдвиг строк по памяти по сигналу sdwig, транспонирование блоков раз в 256 тактов и двухуровневая коррекция с использованием двух параллельных ВСН-декодеров — обеспечивает реализацию непрерывного декодирования фреймов СІ-ВСН. В результате декодер способен исправлять как случайные ошибки, так и протяжённые пакеты ошибок, сохраняя устойчивую производительность при потоковой обработке данных.

# Оценка помехоустойчивости

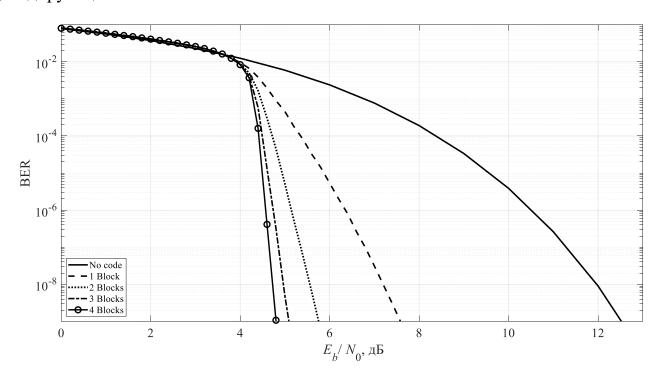

На рисунке 5 представлена зависимость вероятности битовой ошибки (BER) от отношения энергии бита к спектральной плотности шума ( $E_b/N_0$ ) для модуляции BPSK [25] и кода CI-BCH с разным количеством каскадно соединённых декодирующих блоков.

Рисунок 5 — Теоретическая зависимость вероятности ошибки на бит от отношения  $E_b/N_0$  для предложенной реализации декодера кода CI-BCH и их каскадного

включения

Кривая «No code» соответствует передаче без применения коррекции ошибок. В этом случае BER убывает экспоненциально с ростом  $E_b/N_0$ , что отражает стандартное поведение системы BPSK в канале с аддитивным белым гауссовским шумом [26].

Кривые показывают эффективность применения CI-BCH-кода с разным количеством каскадно соединённых декодирующих блоков. Видно, что уже при

одном декодере достигается значительное снижение BER по сравнению с отсутствием кодирования. Добавление дополнительных декодеров последовательно сдвигает кривую влево, что эквивалентно увеличению ЭВК. При этом в области низких значений BER ( $10^{-6}$ – $10^{-8}$ ) прирост от увеличения количества декодеров становится особенно заметен: каждая дополнительная ступень снижает вероятность ошибки на порядок при меньшем значении  $E_b/N_0$ .

Таким образом, график иллюстрирует ключевую особенность CI-ВСН-кодов — масштабируемость за счёт каскадирования декодеров. Последовательное включение нескольких декодирующих блоков (как реализовано в предложенной микросхеме, где установлено два декодера) позволяет достичь существенно более высокой помехоустойчивости без значительного усложнения архитектуры.

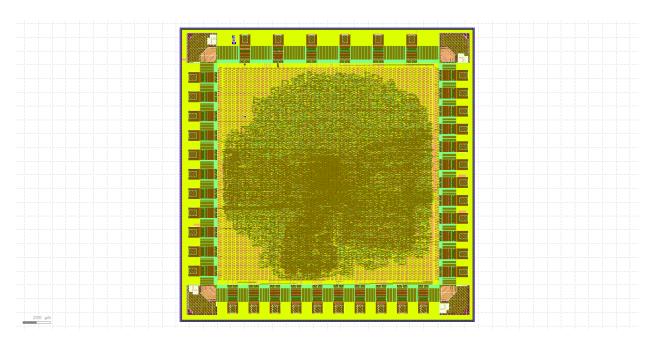

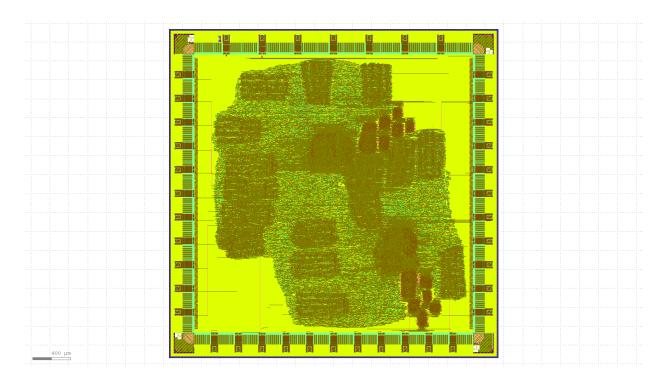

# Результаты

Предложенная архитектура реализована в виде топологии интегральной схемы на основе технологии АО «Микрон» HCMOS8D (КМОП-процесс с топологической нормой 180 нм, шесть уровней металлизации, библиотека стандартных ячеек CORELIB8DLL).

В ходе проектирования и синтеза достигнуты следующие параметры:

- Напряжение питания 1,8 В.

- Тактовая частота 100 МГц.

- Пропускная способность 1,6 Гбит/с.

- Потребляемый ток не более 5 мА.

Аппаратные ресурсы – кодер: около 30 тыс. стандартных ячеек; декодер: около 150 тыс. стандартных ячеек.

Достигнутый уровень характеристик разработанной микросхемы согласуется с иными результатами, полученными на данной библиотеке [27-30]

Рисунок 6 – Топология кодера

Рисунок 7 — Топология декодера

#### Выводы

Полученные параметры свидетельствуют о том, что кодер и декодер СІ-ВСН обладают умеренной аппаратной сложностью и низким энергопотреблением. При использовании 180-нм технологии они занимают относительно небольшую площадь, что позволяет без труда интегрировать данные модули в состав более сложных систем-на-кристалле.

Рабочая частота в 100 МГц обеспечивает пропускную способность порядка 1,6 Гбит/с, чего достаточно для применения в широком спектре цифровых каналов связи. При переходе на более современные технологические нормы (например, 90 или 65 нм) возможен значительный рост частоты работы и, как следствие, пропускной способности при сохранении логической структуры.

Низкое энергопотребление (<10 мВт) позволяет использовать микросхему в энергоограниченных приложениях, включая телекоммуникационное оборудование, где требуется обеспечить высокую помехоустойчивость при минимальных затратах энергии. Таким образом, предложенное решение подтверждает практическую реализуемость СІ-ВСН в виде специализированных микросхем.

# Финансирование

Работа была выполнена за счет средств Минобрнауки России в рамках федерального проекта «Подготовка кадров и научного фундамента для электронной промышленности» по гос. заданию на выполнение научно-исследовательской работы «Разработка методики прототипирования электронной компонентной базы на отечественных микроэлектронных производствах на основе сервиса MPW (FSMR-2023-0008)».

# **Funding**

This work was funded by the Ministry of Education and Science of Russia within the federal project «Training of personnel and scientific foundation for the electronics industry» for the state assignment for the implementation of research work «Development of a methodology for prototyping an electronic component base in domestic microelectronic production based on the MPW service (FSMR-2023-0008)».

#### Список источников

- 1. Fejjari A., et al. A Review of Anomaly Detection in Spacecraft Telemetry Data // Applied Sciences. 2025. vol. 15, no. 10. DOI: 10.3390/app15105653. URL: https://www.mdpi.com/2076-3417/15/10/5653 (дата обращения: 10.10.2025).

- 2. Козлов И. В., Набоков С. А., Смирнов А. С. Программа имитационного моделирования цифровых радиолиний передачи данных // Труды МАИ. Вып. 45. URL: https://trudymai.ru/upload/iblock/1cc/programma-imitatsionnogo-modelirovaniya-tsifrovykh-radioliniy-peredachi-dannykh.pdf (дата обращения: 10.10.2025).

- 3. Горностаев А. И. Меры по ослаблению помех на уровне проектирования измерительной системы космических аппаратов // Космическое приборостроение. 2022. Т. 6, № 4 (42). с. 287-302. DOI 10.26732/j.st.2022.4.08. AO «Информационные спутниковые системы» им. акад. М. Ф. Решетнёва» (Железногорск).

- 4. Handbook on Radiocommunication for Space Research (SRS). // ITU-R. Geneva, 2013. URL: https://www.itu.int/dms\_pub/itu-r/opb/hdb/R-HDB-43-2013-OAS-PDF-R.pdf

- 5. Volkov A., Sviridov I. Construction of Algebraic Convolutional Codes Based on Reed-Solomon Generator Polynomials // Systems of Signal Synchronization, Generating and Processing in Telecommunications (SYNCHROINFO 2024): Proceedings of the International Conference, Vyborg, Russian Federation, 2024. pp. 1-6. DOI: 10.1109/SYNCHROINFO61835.2024.10617742.

- Исследование помехоустойчивости систем неортогонального множественного доступа NOMA с разделением по шаблонам / М. Г. Бакулин, Т. Б. К. Бен Режеб, В. Б. Крейнделин и др. // Электросвязь. – 2023. – № 4. – с. 11-17.

- 7. Шевцов В. А., Богданов А. С. Исследование современных адаптивных алгоритмов декодирования сверточных кодов // Информационно-измерительные и управляющие системы. 2006. Т. 4, № 11. с. 65-67. EDN VRPDOA.

- 8. Волков А. С., Крейнделин В. Б. Алгоритмы кодирования алгебраических недвоичных каскадных сверточных кодов уменьшенной сложности // Т-Сотт: Телекоммуникации и транспорт. 2024. Т. 18, № 3. с. 11-18. DOI: 10.36724/2072-8735-2024-18-3-11-18. EDN: YWVJBK.

- 9. Scholten M., Coe T., Dillard J., Chang F. Enhanced FEC for 40G/100G // Proceedings of the European Conference on Optical Communication (ECOC). Vitesse Semiconductor, 2009. 12 p.

- 10. Кузнецов В. С., Волков А. С., Солодков А. В., Лоос В. В. Разработка кодека троичного кода // Труды МАИ. 2024. № 139. URL: https://trudymai.ru/published.php?ID=183459 (дата обращения: 10.10.2025).

- 11. ITU-T. Recommendation G.975.1: Forward error correction for high bit-rate DWDM submarine systems. Geneva: International Telecommunication Union, 2004. 52 p.

- 12. Lin S., Costello D. J. Jr. Channel Codes: Classical and Modern. Cambridge: Cambridge University Press, 2009. 885 p. ISBN 978-0-521-89596-4.

- 13. Scholten M., Coe T., Dillard J. Continuously-Interleaved BCH (CI-BCH) FEC delivers best in class NECG for 40G and 100G metro applications // Proceedings of the Optical Fiber Communication Conference (OFC/NFOEC 2010). Optical Society of America, 2010. Paper NTuB3.

- 14. Yu F., Li M., Stojanovic N., Xie C., Xiao Z., Li L. FPGA Demonstration of Stretched Continuously Interleaved BCH Code with Low Error Floor for Short-Range Optical Transmission // Optical Fiber Communication Conference: OSA Technical Digest (online).

- Optica Publishing Group, 2017. Paper W1J.5. URL:

https://opg.optica.org/abstract.cfm?URI=OFC-2017-W1J.5 (дата обращения:

10.10.2025).

- 15. Rieger M. Application Specific Integrated Circuits (ASICs) // The Electronic Design Automation Handbook / ed. by M. Rieger. Boston: Springer, 2003. c. 384-397. DOI: 10.1007/978-0-387-73543-6\_16.

- 16. Azadet K., Haratsch E. F., Kim H., Saibi F., Saunders J. H., Shaffer M., Song L., Yu M.-L. Equalization and FEC Techniques for Optical Transceivers // IEEE Journal of Solid-State Circuits. 2002. vol. 37, no. 3. pp. 317-327. DOI: 10.1109/4.987099.

- 17. Волков А. С., Солодков А. В. Разработка топологии интегральной микросхемы кодека алгебраического сверточного кода // Труды МАИ. 2023. № 133. URL: https://trudymai.ru/published.php?ID=183205 (дата обращения: 10.10.2025). EDN: PJKLFV.

- 18. Shi Y. Q., Zhang X. M., Ni Z.-C., Ansari N. Interleaving for Combating Bursts of Errors // IEEE Circuits & Systems Magazine. 2004. vol. 4, no. 1. pp. 29-42. DOI: 10.1109/MCAS.2004.1286985. URL: https://web.njit.edu/anl/papers/04CASMag.pdf (дата обращения: 10.10.2025).

- 19. Scholten M., Coe T., Dillard J. Continuously-Interleaved BCH (CI-BCH) FEC delivers best-in-class NECG for 40G and 100G metro applications // Proceedings of the Optical Fiber Communication Conference (OFC/NFOEC 2010). Optical Society of America, 2010. Paper NTuB3. URL: https://opg.optica.org/abstract.cfm?uri=OFC-2010-NTuB3 (дата обращения: 10.10.2025).

- 20. Roth C. H., John L. K., Lee B. K. Digital Systems Design Using Verilog. Boston: Cengage Learning, 2015. 824 p. ISBN 978-1-305-25333-3.

- 21. Mohammad M. An 8b/10b Encoding Serializer/Deserializer (SerDes) Circuit for High Speed Communication Applications Using a DC Balanced, Partitioned Block, 8b/10b Transmission Code // International Journal of Electronics and Electrical Engineering, April, 2015. vol. 3, no. 2. URL: https://www.researchgate.net/profile/Mohammad-Maadi/publication/263469266\_An\_8b10b\_Encoding\_SerializerDeserializer\_SerDes\_Circuit\_for\_High\_Speed\_Communication\_Applications\_Using\_a\_DC\_Balanced\_Partitioned-Block\_8b10b\_T/links/00b4953b02347b64fb000000/An-8b-10b-Encoding-Serializer-Deserializer-SerDes-Circuit-for-High-Speed-Communication-Applications-Using-a-DC-Balanced-Partitioned-Block-8b-10b-T.pdf (дата обращения: 10.10.2025).

- 22. Shi Y. Q., Zhang X. M., Ni Z. C., Ansari N. Interleaving for Combating Bursts of Errors // IEEE Circuits & Systems Magazine. 2004. vol. 4, no. 1. pp. 29-42. DOI: 10.1109/MCAS.2004.1286985.

- 23. Huffman W. C., Pless V. Fundamentals of Error-Correcting Codes. Cambridge: Cambridge University Press, 2003. 646 p. ISBN 0-521-78280-5.

- 24. Волков А. С. Разработка имитационной модели канала с группирующимися ошибками // Труды МАИ: сетевое научное издание. М.: МАИ, 2023. № 128. 31 с. DOI: 10.34759/trd-2023-128-12. URL: https://trudymai.ru/published.php?ID=183120 (дата обращения: 10.10.2025).

- 25. Sklar B. Digital Communications: Fundamentals and Applications: монография. 2nd edition Upper Saddle River: Prentice Hall, 2001. 1104 p. ISBN 0-13-084788-7.

- 26. Прокис Дж. Г. Цифровая связь 4-е изд. M.: Радио и связь, 2006. 928 с.

- 27. Свидетельство о государственной регистрации топологии микросхемы № 2025630088 Российская Федерация. Топология интегральной микросхемы приемопередатчика с троичным помехоустойчивым кодом и модуляцией на троичном базисе: заявл. 28.03.2025: опубл. 04.04.2025 / А. С. Волков, В. В. Лоос, А. В. Витвинов. EDN IJISNA.

- 28. Свидетельство о государственной регистрации топологии интегральной микросхемы № 2025630088 РФ. Топология интегральной микросхемы приемопередатчика с троичным помехоустойчивым кодом и модуляцией на троичном базисе: заявл. 28.03.2025: опубл. 04.04.2025 / А. С. Волков, В. В. Лоос, А. В. Витвинов. EDN: IJISNA.

- 29. Свидетельство о государственной регистрации топологии интегральной микросхемы № 2024630220 РФ. Микросхема блоков модема на основе алгебраического сверточного кода: № 2024630217: заявл. 15.10.2024; опубл. 21.10.2024 / И. А. Свиридов, А. С. Волков, А. В. Солодков [и др.]; заявитель:

Национальный исследовательский университет «Московский институт электронной техники». – EDN: LFMEBY.

30. Свидетельство о государственной регистрации топологии интегральной микросхемы № 2023630211 РФ. Топология микросхемы совмещенного кодека алгебраического сверточного и блокового кода с возможностью перемежения: № 2023630231: заявл. 15.11.2023; опубл. 20.11.2023 / А. С. Волков, А. В. Солодков, И.А. Свиридов; заявитель: Национальный исследовательский университет «Московский институт электронной техники». — EDN: XCDNQG.

# References

- 1. Fejjari, A., et al. (2025). A Review of Anomaly Detection in Spacecraft Telemetry Data. Applied Sciences, 15(10). DOI: 10.3390/app15105653, URL: https://www.mdpi.com/2076-3417/15/10/5653, accessed 10 October 2025.

- 2. Kozlov, I. V., Nabokov, S. A., Smirnov, A. S. *Programma imitacionnogo modelirovaniya cifrovyh radioliniy peredachi dannyh* (Simulation Program for Digital Radio Communication Lines). *Trudy MAI* (Proceedings of MAI), 45. Retrieved from https://trudymai.ru/upload/iblock/1cc/programma-imitatsionnogo-modelirovaniyatsifrovykh-radioliniy-peredachi-dannykh.pdf, accessed 10 October 2025.

- 3. Gornostayev, A. I. *Mery po oslableniyu pomeh na urovne proektirovaniya izmeritelnoy sistemy kosmicheskih apparatov* (Measures to Reduce Interference at the Design Level of Spacecraft Measuring Systems). *Kosmicheskoe Priborostroenie* (Space Instrumentation), vol. 6, no 4(42), pp. 287-302. DOI: 10.26732/j.st.2022.4.08

- 4.International Telecommunication Union. Handbook on Radiocommunication for Space Research (SRS). Geneva: ITU-R, 2013. 240 c.

- 5. Volkov A. S., Sviridov I. A. Construction of Algebraic Convolutional Codes Based on Reed–Solomon Generator Polynomials, Proceedings of the Systems of Signal Synchronization, Generating and Processing in Telecommunications (SYNCHROINFO 2024), Vyborg, Russian Federation, 2024, pp. 1-6, DOI: 10.1109/SYNCHROINFO61835.2024.10617742.

- 6. Bakulin M. G., Ben Rejeb T. B. K., Kreindelin V. B. et al., *Issledovanie pomekhoustoichivosti sistem neortogonal'nogo mnozhestvennogo dostupa NOMA s razdeleniem po shablonam* (Investigation of Noise Immunity in NOMA Systems with Pattern Division), *Elektrosvyaz* (Telecommunication), 2023, no. 4, pp. 11-17, DOI: 10.34832/ELSV2023.41.4.002, EDN: BNPMGG.

- 7. Shevtsov V. A., Bogdanov A. S., *Issledovanie sovremennykh adaptivnykh algoritmov dekodirovaniya svertochnykh kodov* (Study of Modern Adaptive Algorithms for Convolutional Code Decoding), Information-Measuring and Control Systems, 2006, vol. 4, no. 11, pp. 65-67, EDN: VRPDOA.

- 8. Volkov A. S., Kreindelin V. B., *Algoritmy kodirovaniya algebraicheskikh nedvoichnykh kaskadnykh svertochnykh kodov umenshennoi slozhnosti* (Algorithms for Encoding Algebraic Non-binary Cascaded Convolutional Codes of Reduced Complexity), T-Comm: Telecommunications and Transport, 2024, vol. 18, no. 3, pp. 11-18, DOI: 10.36724/2072-8735-2024-18-3-11-18, EDN: YWVJBK.

- 9. Scholten M., Coe T., Dillard J., Chang F., Enhanced FEC for 40G/100G, Proceedings of the European Conference on Optical Communication (ECOC), Vitesse Semiconductor, 2009, 12 p.

- 10. Kuznetsov V. S., Volkov A. S., Solodkov A. V., Loos V. V., *Razrabotka kodeka troichnogo koda* (Codec design for ternary code), *Trudy MAI* (Proceedings of MAI), 2024, no. 139, URL: https://trudymai.ru/published.php?ID=183459, accessed 10 October 2025.

- 11. ITU-T, Recommendation G.975.1: Forward Error Correction for High Bit-Rate DWDM Submarine Systems, Geneva, International Telecommunication Union, 2004, 52 p.

- 12. Lin S., Costello D. J. Jr., Channel Codes: Classical and Modern, Cambridge, Cambridge University Press, 2009, 885 p., ISBN 978-0-521-89596-4.

- 13. Scholten M., Coe T., Dillard J., Continuously-Interleaved BCH (CI-BCH) FEC delivers best in class NECG for 40G and 100G metro applications, Proceedings of the Optical Fiber Communication Conference (OFC/NFOEC 2010), Optical Society of America, 2010, Paper NTuB3.

- 14. Yu F., Li M., Stojanovic N., Xie C., Xiao Z., Li L., FPGA Demonstration of Stretched Continuously Interleaved BCH Code with Low Error Floor for Short-Range Optical Transmission, Optical Fiber Communication Conference: OSA Technical Digest (online), Optica Publishing Group, 2017, Paper W1J.5, URL: https://opg.optica.org/abstract.cfm?URI=OFC-2017-W1J.5, accessed 10 October 2025.

- 15. Rieger M., Application Specific Integrated Circuits (ASICs), The Electronic Design Automation Handbook, Boston, Springer, 2003, pp. 384-397, DOI: 10.1007/978-0-387-73543-6\_16.

- 16. Azadet K., Haratsch E. F., Kim H., Saibi F., Saunders J. H., Shaffer M., Song L., Yu M.-L., Equalization and FEC Techniques for Optical Transceivers, IEEE Journal of Solid-State Circuits, 2002, vol. 37, no. 3, pp. 317-327, DOI: 10.1109/4.987099.

- 17. Volkov A. S., Solodkov A. V., *Razrabotka topologii integral'noi mikroskhemy kodeka algebraicheskogo svertochnogo koda* (Design of an integrated circuit topology for an algebraic convolutional codec), *Trudy MAI* (Proceedings of MAI), 2023, no. 133, URL: https://trudymai.ru/published.php?ID=183205, accessed 10 October 2025, EDN: PJKLFV. 18. Shi Y. Q., Zhang X. M., Ni Z.-C., Ansari N., Interleaving for Combating Bursts of Errors, IEEE Circuits & Systems Magazine, 2004, vol. 4, no. 1, P. 29–42, DOI: 10.1109/MCAS.2004.1286985, URL: https://web.njit.edu/anl/papers/04CASMag.pdf, accessed 10 October 2025.

- 19. Scholten M., Coe T., Dillard J., Continuously-Interleaved BCH (CI-BCH) FEC Delivers Best-in-Class NECG for 40G and 100G Metro Applications, Proceedings of the Optical Fiber Communication Conference (OFC/NFOEC 2010), Optical Society of America, 2010, Paper NTuB3, URL: https://opg.optica.org/abstract.cfm?uri=OFC-2010-NTuB3, accessed 10 October 2025.

- 20. Roth C. H., John L. K., Lee B. K., Digital Systems Design Using Verilog, Boston, Cengage Learning, 2015, 824 p., ISBN 978-1-305-25333-3.

- 21. Mohammad M., An 8b/10b Encoding Serializer/Deserializer (SerDes) Circuit for High Speed Communication Applications Using a DC Balanced, Partitioned Block, 8b/10b Transmission Code, International Journal of Electronics and Electrical Engineering, 2015, vol. 3, no. 2, April, URL: https://www.researchgate.net/profile/Mohammad-Maadi/publication/263469266 An 8b10b Encoding SerializerDeserializer SerDes Circu

- it\_for\_High\_Speed\_Communication\_Applications\_Using\_a\_DC\_Balanced\_Partitioned-Block\_8b-10b\_T/links/00b4953b02347b64fb000000/An-8b-10b-Encoding-Serializer-Deserializer-SerDes-Circuit-for-High-Speed-Communication-Applications-Using-a-DC-Balanced-Partitioned-Block-8b-10b-T.pdf, accessed 10 October 2025.

- 22. Shi Y. Q., Zhang X. M., Ni Z. C., Ansari N., Interleaving for Combating Bursts of Errors, IEEE Circuits & Systems Magazine, 2004, vol. 4, no. 1, pp. 29-42, DOI: 10.1109/MCAS.2004.1286985.

- 23. Huffman W. C., Pless V., Fundamentals of Error-Correcting Codes, Cambridge, Cambridge University Press, 2003, 646 p., ISBN 0-521-78280-5.

- 24. Volkov A. S., *Razrabotka imitatsionnoi modeli kanala s grupiruyushchimisya oshibkami* (The development of simulation model of channel with burst error arrays), *Trudy MAI* (Proceedings of MAI), Moscow, MAI, 2023, no. 128, 31 p., DOI: 10.34759/trd-2023-128-12, URL: https://trudymai.ru/published.php?ID=183120, accessed 10 October 2025.

- 25. Sklar B., Digital Communications: Fundamentals and Applications, 2nd ed., Upper Saddle River, Prentice Hall, 2001, 1104 p., ISBN 0-13-084788-7.

- 26. Proakis J. G., *Tsifrovaya svyaz'* (Digital Communications), 4-e izd., Moscow, Radio i Svyaz', 2006, 928 p.

- 27. Certificate of State Registration of Integrated Circuit Topology no. 2025630088 (Russian Federation), Topology of the Integrated Circuit Transceiver with a Ternary Error-Correcting Code and Modulation on a Ternary Basis, appl. 28 Mar 2025, publ. 04 Apr 2025, Volkov A. S., Loos V. V., Vitvinov A. V., EDN: IJISNA.

- 28. Certificate of State Registration of Integrated Circuit Topology no. 2025630088 (Russian Federation), Topology of the Integrated Circuit Transceiver with a Ternary Error-

- Correcting Code and Modulation on a Ternary Basis, appl. 28 Mar 2025, publ. 04 Apr 2025, Volkov A. S., Loos V. V., Vitvinov A. V., EDN: IJISNA.

- 29. Certificate of State Registration of Integrated Circuit Topology no. 2024630220 (Russian Federation), Integrated Circuit of Modem Blocks Based on Algebraic Convolutional Code, no. 2024630217, appl. 15 Oct 2024, publ. 21 Oct 2024, Sviridov I. A., Volkov A. S., Solodkov A. V. et al., applicant: National Research University of Electronic Technology MIET, EDN: LFMEBY.

- 30. Certificate of State Registration of Integrated Circuit Topology no. 2023630211 (Russian Federation), Topology of the Integrated Circuit of a Combined Codec of Algebraic Convolutional and Block Codes with Interleaving Capability, no. 2023630231, appl. 15 Nov 2023, publ. 20 Nov 2023, Volkov A. S., Solodkov A. V., Sviridov I. A., applicant: National Research University of Electronic Technology MIET, EDN: XCDNQG.